# Thriving in the world of high-speed serial interconnects

#### July 16, 2003

presented by:

#### **Art Porter**

© Copyright 2003 Agilent Technologies, Inc.

- Introduction

- Design stage

- Electrical faults

- Statistics

- PCI Express example

- Real-life examples

- Tools for success

#### Goals

- Meet objectives for performance and reliability

- Finish your project on time and in budget

In the new world of highspeed serial interconnects

**Agilent Technologies**

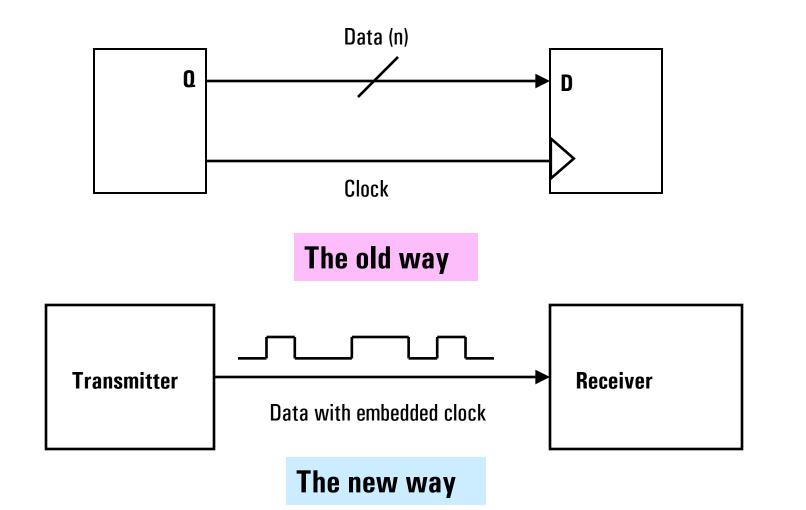

#### **Serial Data With Embedded Clock**

#### **Abstractions**

- Physical layer (signal integrity)

- Protocol

- Data transfer

## **Critical Skills and Tools Required**

- Circuit design and analysis

- Lumped parameters (R/L/C)

- Transmission lines (s-parameters)

- Statistics

- Measurement

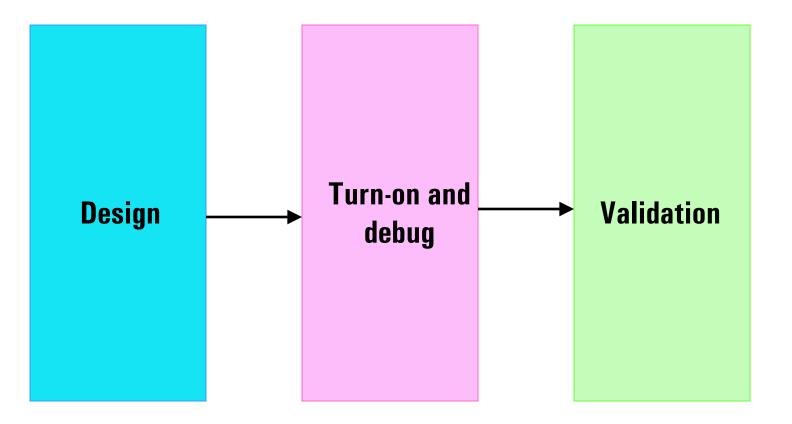

- Introduction

- Design stage

- Electrical faults

- Statistics

- PCI Express example

- Real-life examples

- Tools for success

- The circuit now includes everything

- PC board traces

- Vias

- Pins

- Connectors

- Bond wires

- Metallization

#### Models

- Good designs start with good models

- Good models start with good measurements

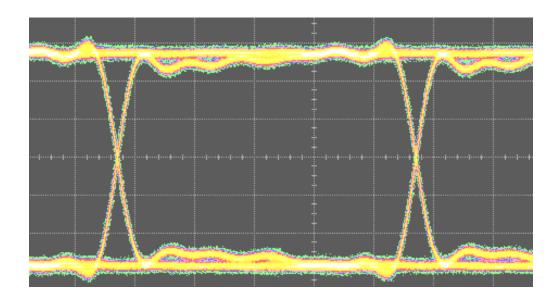

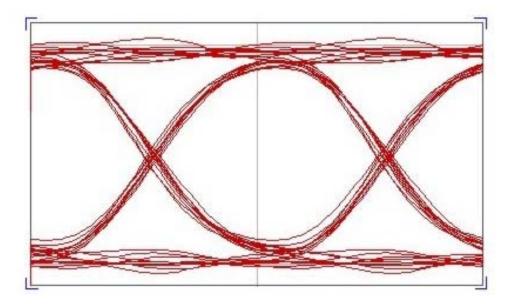

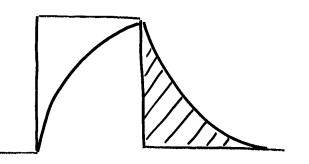

Simulated eye diagram from an Agilent Physical Layer Test System

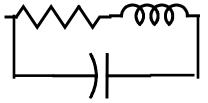

#### Models – What's In a Model?

- Every R has some C and L

- Every C has some L

- If the manufacturer won't or can't give you accurate models, you may have to create them.

What you thought you had

#### Models – What's In a Model?

- Every R has some C and L

- Every C has some L

- If the manufacturer won't or can't give you accurate models, you may have to create them.

What you really have

## **Models – Which To Use?**

- Don't assume model parameters published by trade associations

- Allow for multiple vendors, process changes by simulating with worst-case models

- For transmission lines, decide if you need

- Single-element

- Multi-section, lumped-parameter

- Full transmission line

- Introduction

- Design stage

- Electrical faults

- Statistics

- PCI Express example

- Real-life examples

- Tools for success

# **Types Of Faults**

- Single-net faults

- Multiple-net faults (crosstalk)

- Power and ground faults

## **Single-Net Faults**

- Reflections

- Over or under-damping

- Loss

- Dispersion

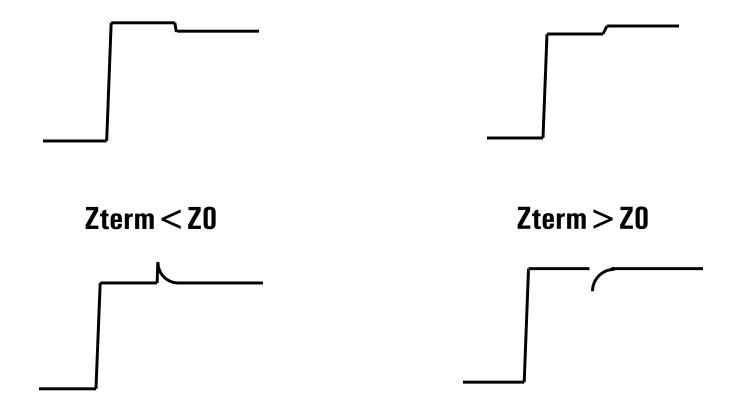

#### Reflections

Inductive discontinuity

#### **Capacitive discontinuity**

## **Avoiding Reflections**

- Start with good models

- Validate models

- Validate structure using TDR or VNA

- Hint: Use the driver and your scope as a TDR

## **Fun With Frequency**

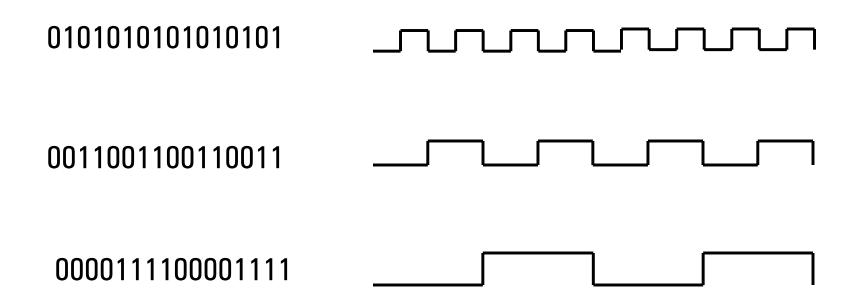

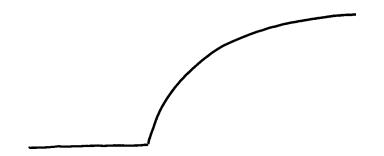

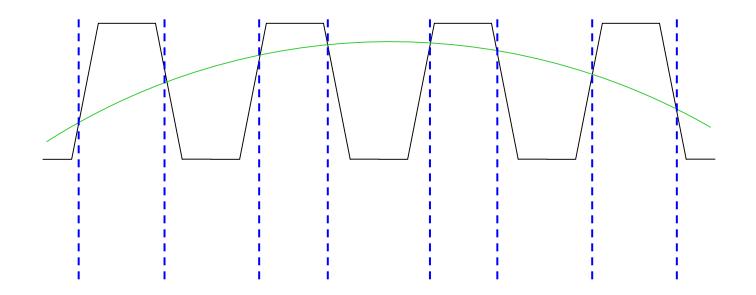

## **Intersymbol Interference (ISI)**

Single-pole RC time constant

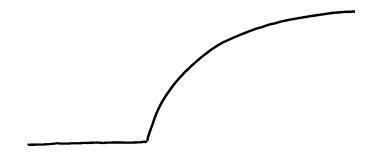

## **Intersymbol Interference (ISI)**

Single-pole RC time constant

Effect on an isolated "1"

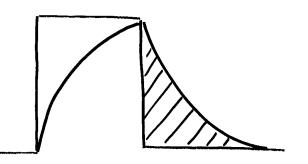

## **Intersymbol Interference (ISI)**

Single-pole RC time constant

Effect on an isolated "1"

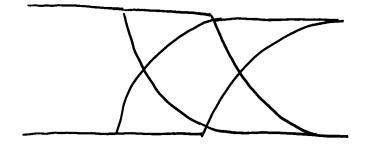

Effect on data eye

## Likely Causes Of ISI

- Over or underdamping

- Dispersion

- Reflections

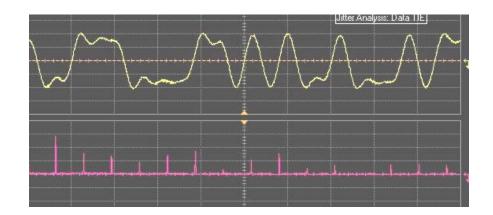

In a PRBS sequence (pseudorandom binary sequence), ISI will exhibit energy peaks in the jitter spectrum at multiples of F/2(sequence length), where F = bit rate.

If possible, try varying PRBS sequence lengths and watch for changes in the jitter spectrum.

#### **Multiple-Net Faults - Crosstalk**

- Can be difficult to distinguish from power and ground coupling phenomena

- Often gets translated into jitter

## **Crosstalk Sleuthing**

- Should show up in the spectrum

- Histogram will be non-Gaussian

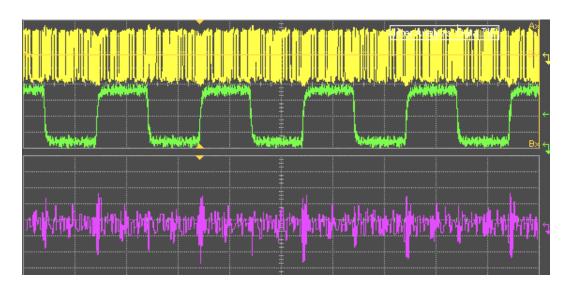

- Try triggering on suspected source

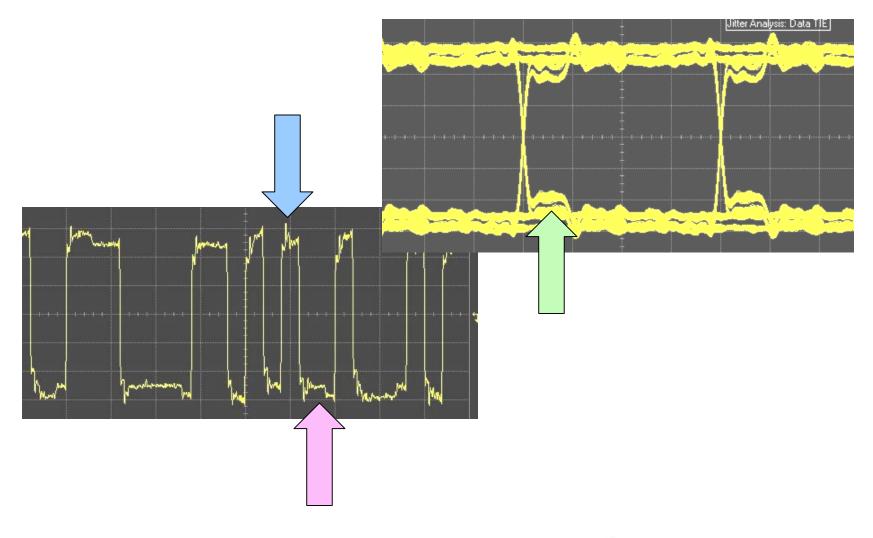

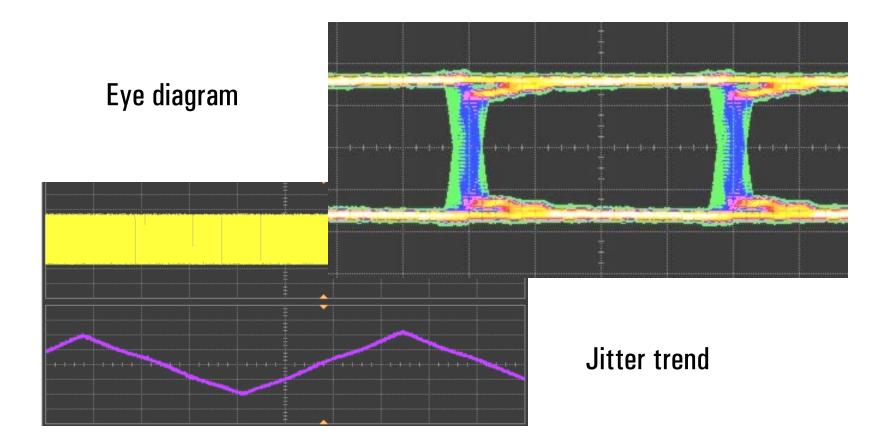

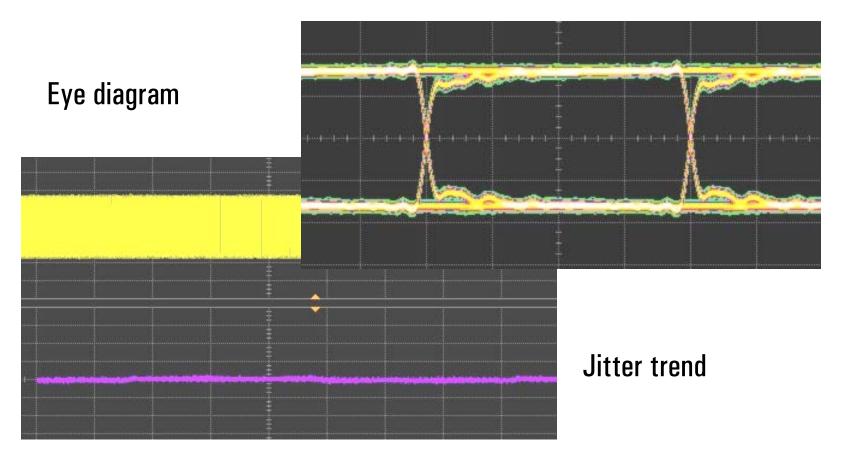

Yellow: signal with jitter

Green: Offending source of jitter

Purple: Jitter trend

#### **Power And Ground**

- Sometimes difficult to distinguish from crosstalk

- Indicator: Affects many or all nodes

- Power and ground faults can impact output delays, thus adding jitter

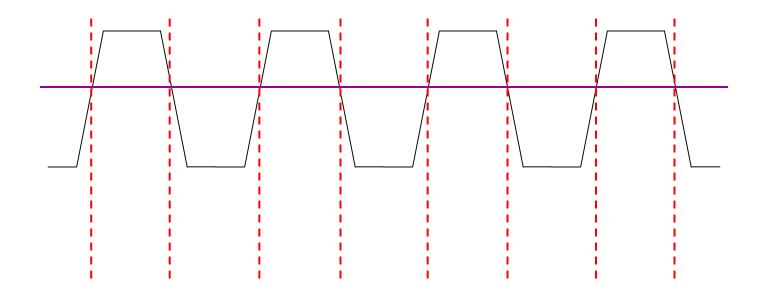

#### **Translating Noise To Jitter**

Constant threshold at the proper level

#### **Translating Noise To Jitter**

Varying threshold

- Introduction

- Design stage

- Electrical faults

- Statistics

- PCI Express example

- Real-life examples

- Tools for success

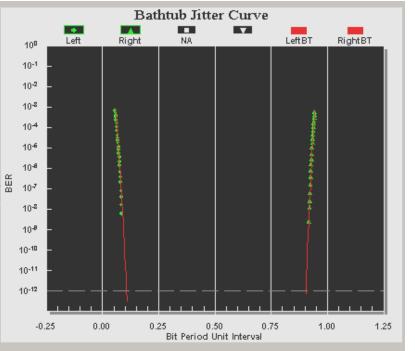

The question is not: Did it pass?

The questions are:

- What is the failure rate?

- How much margin do I have?

#### **Statistics**

- Determine target BER

- Decide on an acceptable confidence

interval

- Introduction

- Design stage

- Electrical faults

- Statistics

- PCI Express example

- Real-life examples

- Tools for success

#### **PCI Express Measurement Example**

- Need to recover clock from the data stream

- PCI Express is differential

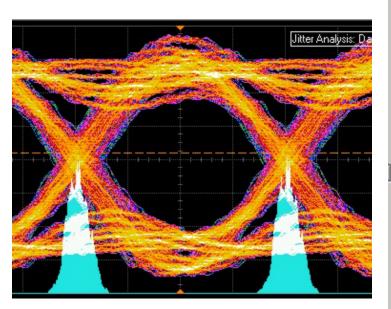

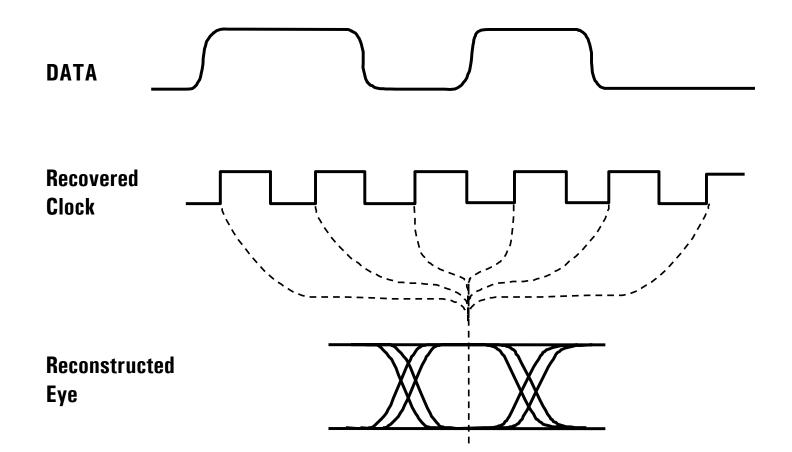

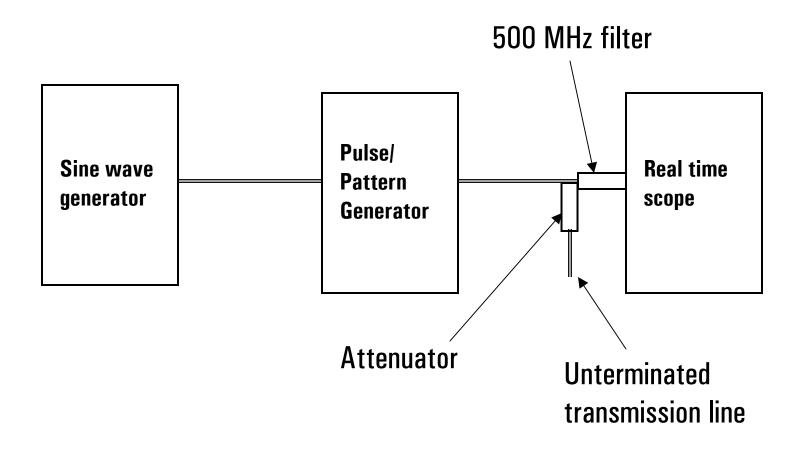

#### **Reconstructing the Eye**

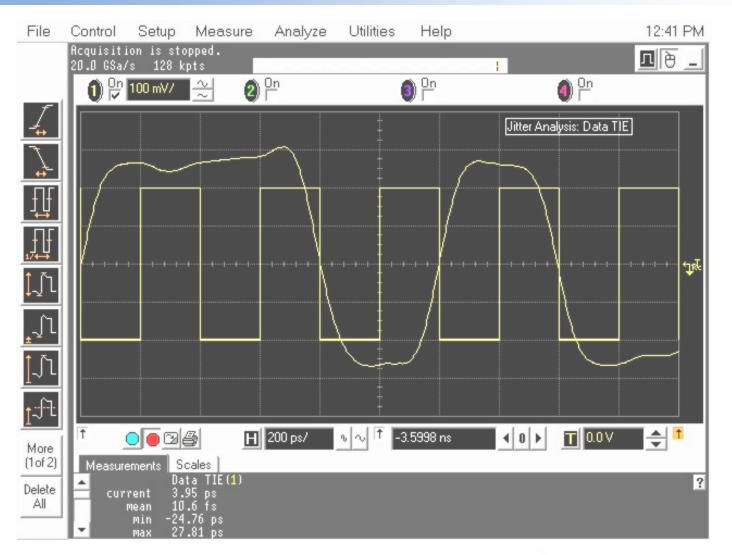

## **PCI Express Showing Clock**

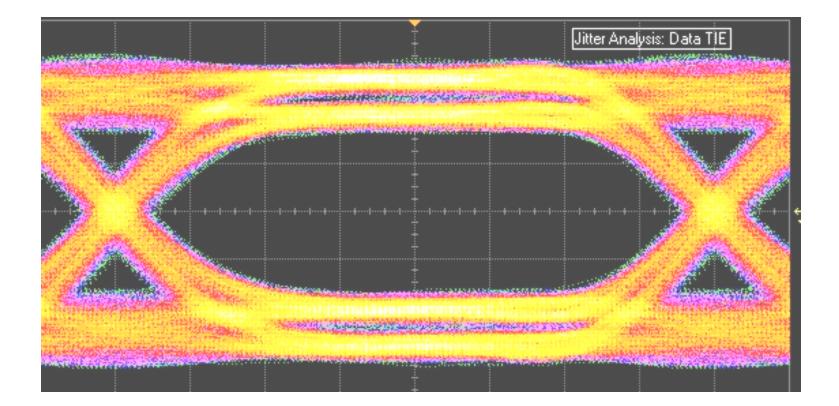

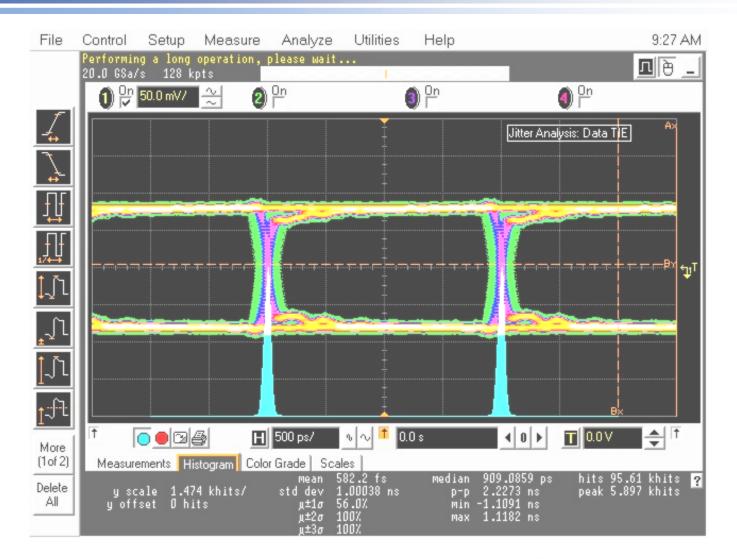

#### **PCI Express Eye, Color Graded**

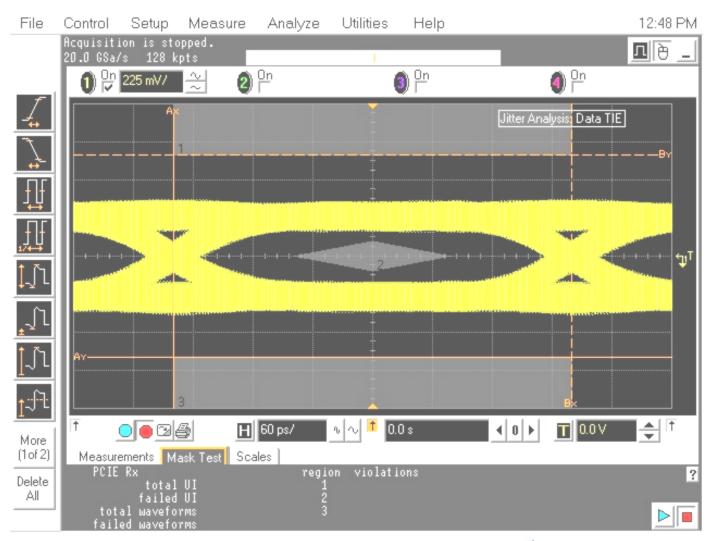

## **PCI Express Eye With Mask**

## **PCI Express, Finding Worst Cases**

## **PCI Express, Finding Worst Cases**

- Introduction

- Design stage

- Electrical faults

- Statistics

- PCI Express example

- Real-life examples

- Tools for success

## **Real life examples**

- ISI

- Band-limiting

- Reflections

- Deterministic, periodic jitter

- Random jitter

- All of the above

- Duty cycle distortion

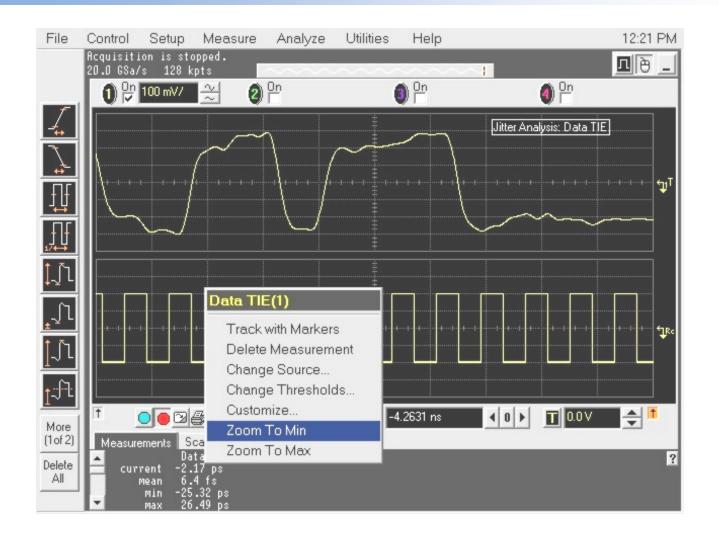

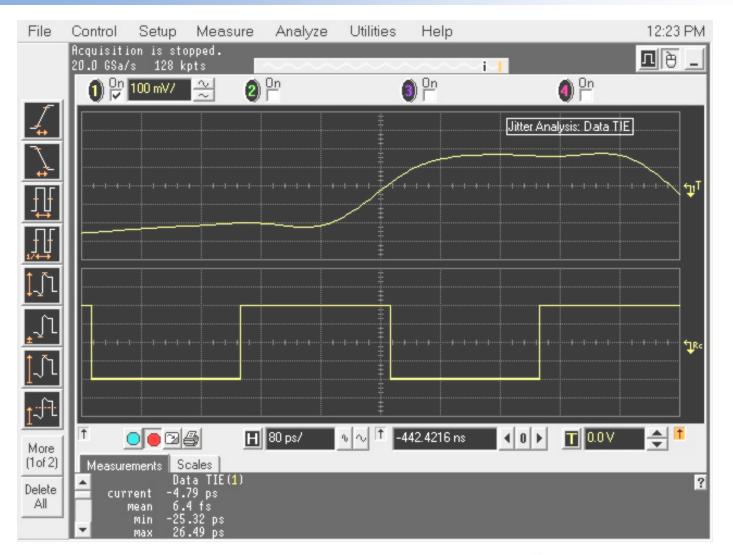

#### **Setup For Examples**

#### **Reference: 500 Mb/s**

Data stream

#### Reflection

#### **Reflection – Jitter Spectrum**

### **Bandwidth Limiting**

### **BW Limiting + Reflection**

#### **Periodic Jitter**

#### **Periodic Jitter**

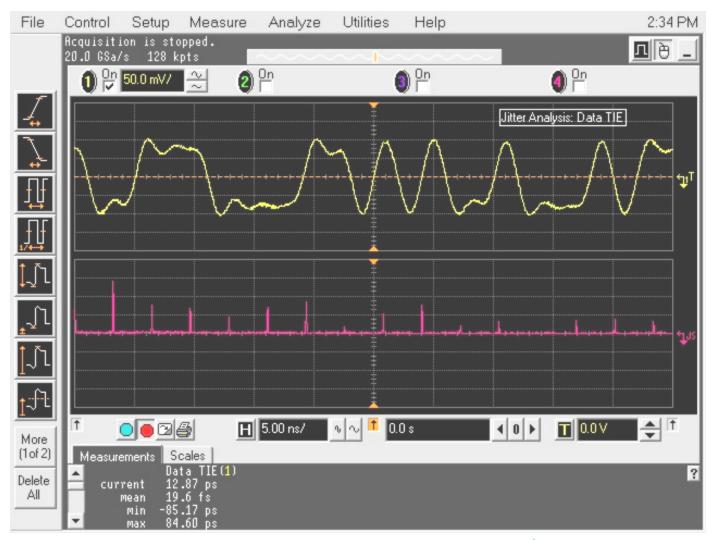

## **Random (Gaussian) Jitter**

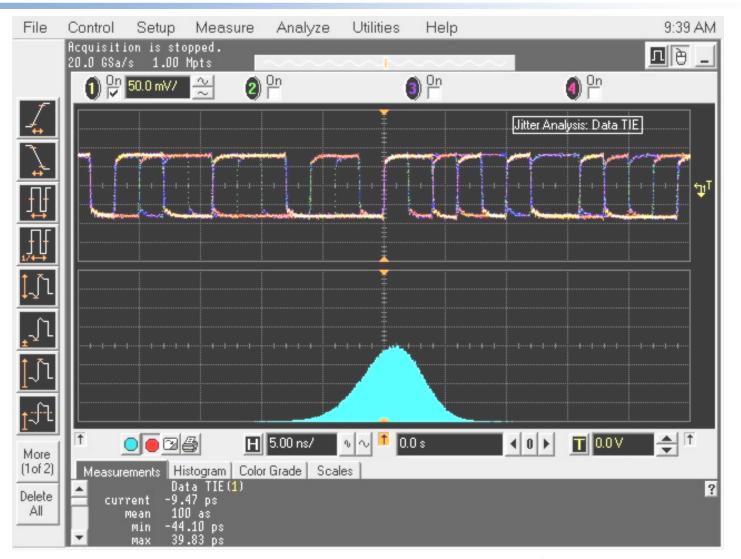

## **Random Jitter – TIE Histogram**

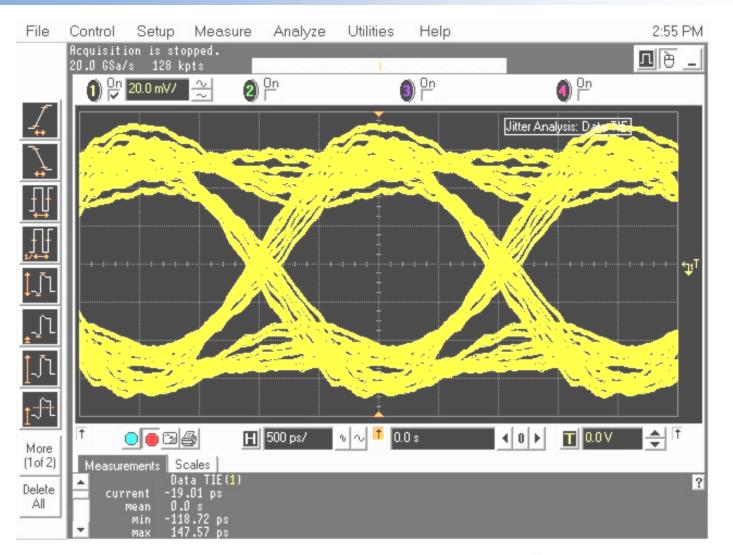

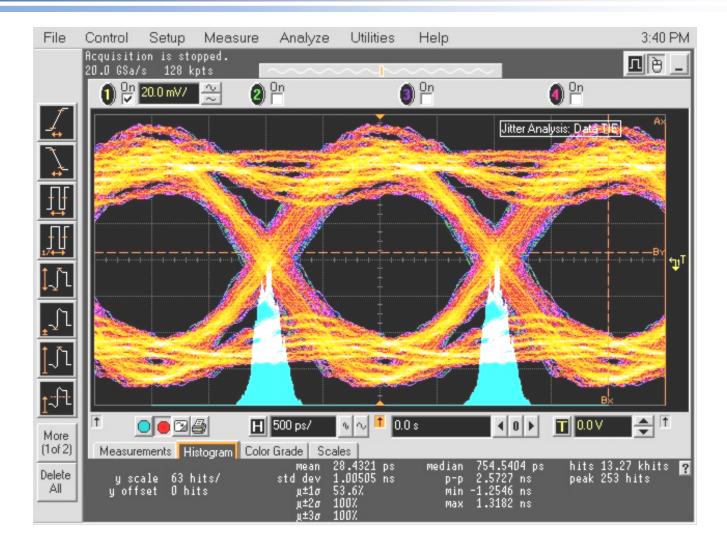

## **All Together Now**

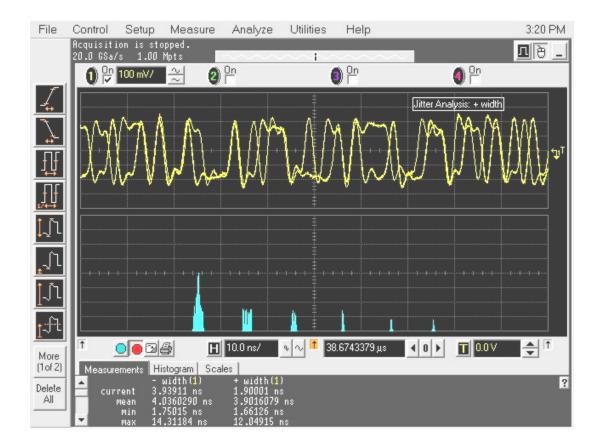

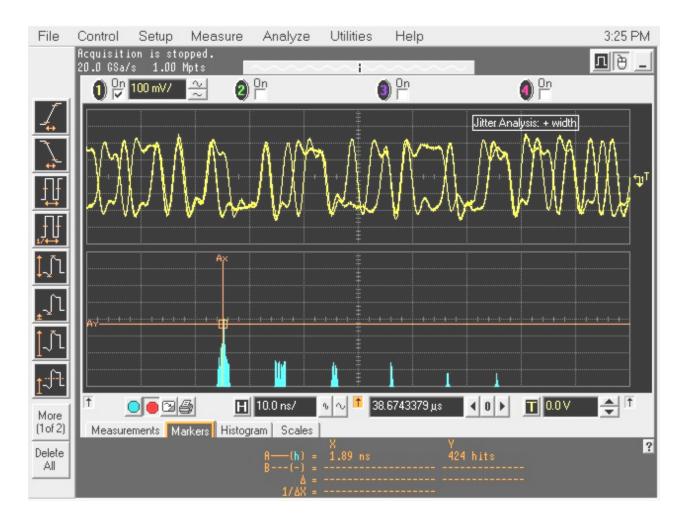

#### **Duty Cycle Distortion - Causes**

- Thresholding effects

- Non-symmetrical delays

- Use jitter measurement

- Measure + and widths

- Analyze histograms

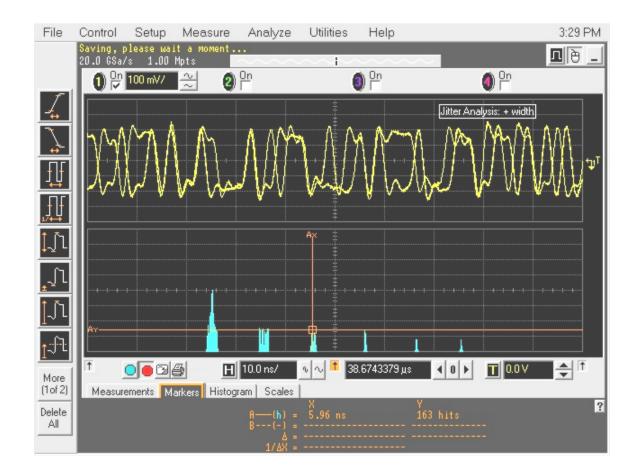

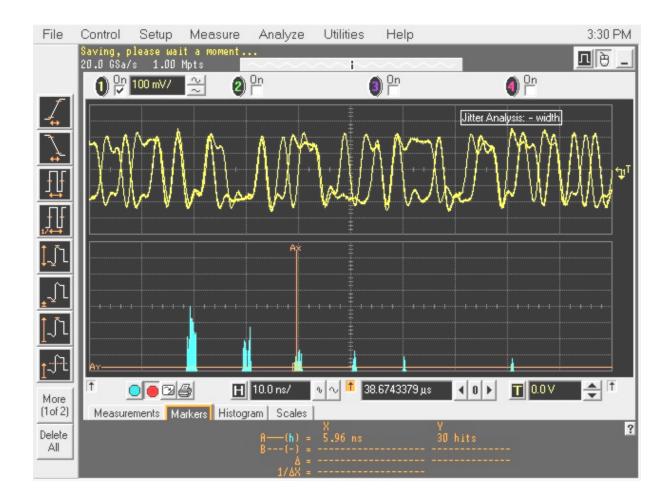

+ width histogram

Measure location of first peak – 1.89 ns

Note location of third peak = 5.96 ns

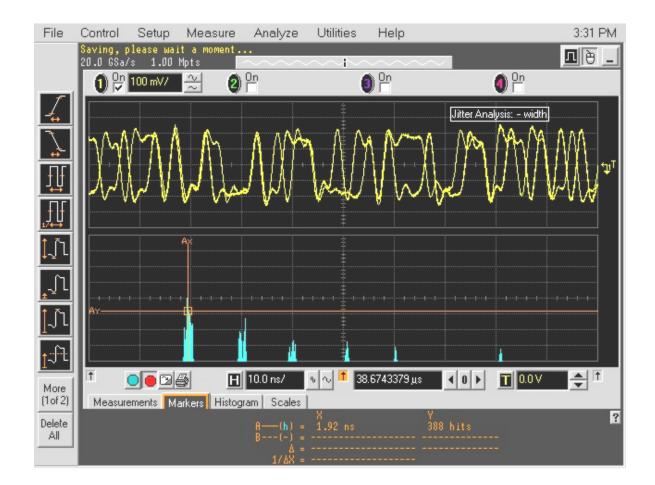

Measure – width, put marker at the same spot, note shift of peak

Same for the third peak

#### **Spread-Spectrum Clocking**

Spread spectrum clocking, without PLL

## **Spread-Spectrum Clocking**

Spread spectrum clocking, with PLL

- Introduction

- Design stage

- Electrical faults

- Statistics

- PCI Express example

- Real-life examples

- Tools for success

#### **Tools For Success**

- Model development and verification – TDR

- VNA, PLTS

- Verification, troubleshooting

- Scope

- Pulse/pattern generator

- Verification

- BERT

#### **Critical Parameters In a Scope**

- Probing

- Time base stability

- Signal tracking accuracy at high speeds

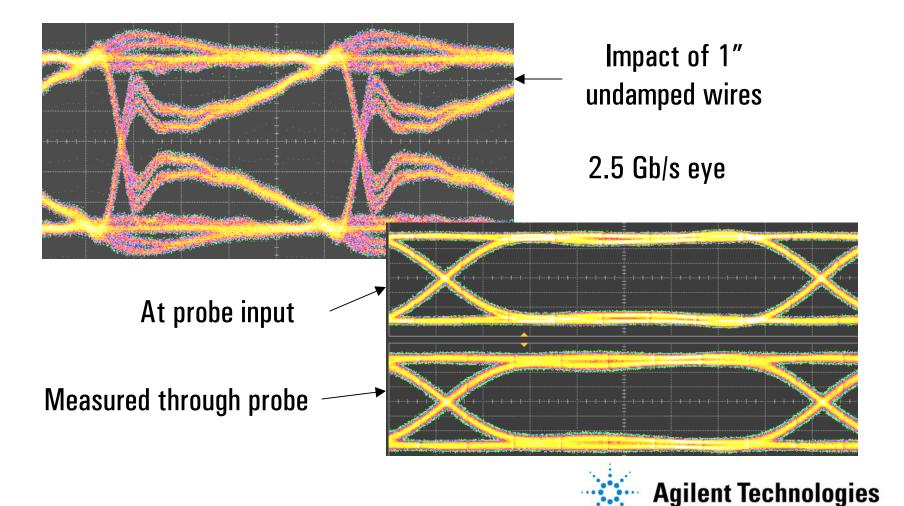

#### **Probes Are Critical**

#### Accurate measurements have to start at the probe tips

#### **Realtime Scope Measurement Tools**

- Serial data analysis (e.g. Agilent E2688A)

- Jitter analysis

- Agilent EZJIT

- M1 Time Interval and Jitter Analysis

## Summary

- Start with good models

- Understand statistical behavior

- Measure everything

- Know your tools

www.agilent.com/find/si

http://www.agilent.com/find/jitter

## **FREE Agilent Email Updates**

#### Subscribe Today!

Choose the information YOU want.

Change your preferences or unsubscribe anytime.

#### Keep up to date on:

#### **Services and Support Information**

- Firmware updates

- Manuals

- Education and training courses

- Calibration

- Additional services

#### **Events and Announcement**

- New product announcement

- Technology information

- Application and product notes

- Seminars and Tradeshows

- eSeminars

#### Go To: www.agilent.com/find/eseminar-email